## EE 435

#### Lecture 18

- Moving the RHP zero into LHP in Miller

Compensated Amplifier

- Breaking the Loop for Loop Gain Analysis

- Op Amp Simulation

- Other Methods of Gain Enhancement

. • • • • Review from last lecture . • • • •

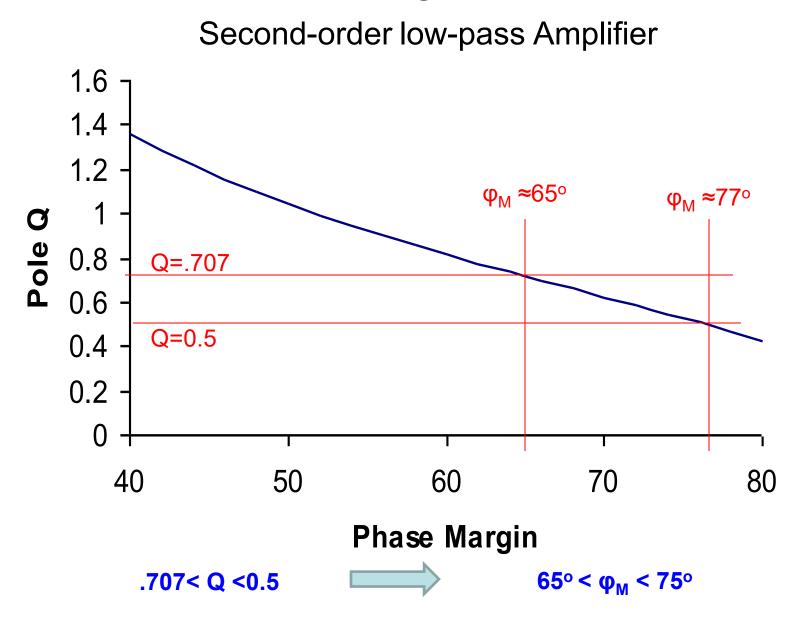

#### Phase Margin vs Q

• • • • • Review from last lecture .• • • • •

## **Compensation Summary**

- Gain and phase margin performance often strongly dependent upon architecture

- Relationship between overshoot and ringing and phase margin were developed only for 2<sup>nd</sup>-order lowpass gain characteristics and differ dramatically for higher-order structures

- Absolute gain and phase margin criteria are not robust to changes in architecture or order

- It is often difficult to correctly "break the loop" to determine the loop gain Aβ with the correct loading on the loop (will discuss this more later)

• • • • • Review from last lecture .• • • • •

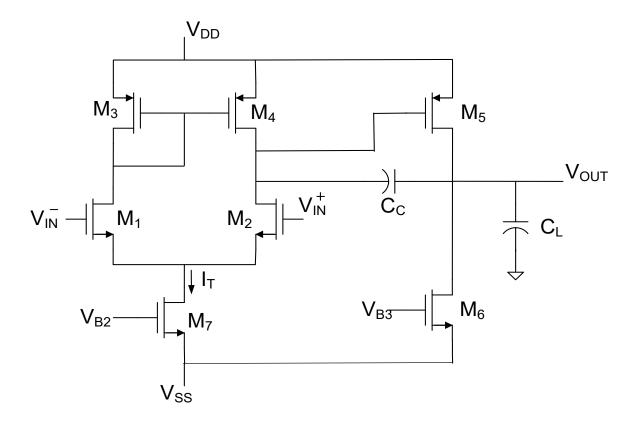

## Design of Two-Stage Op Amps

- Compensation is critical in two-stage op amps

- General approach to designing two-stage op amps is common even though significant differences in performance for different architectures

- Will consider initially the most basic two-stage op amp with internal Miller compensation

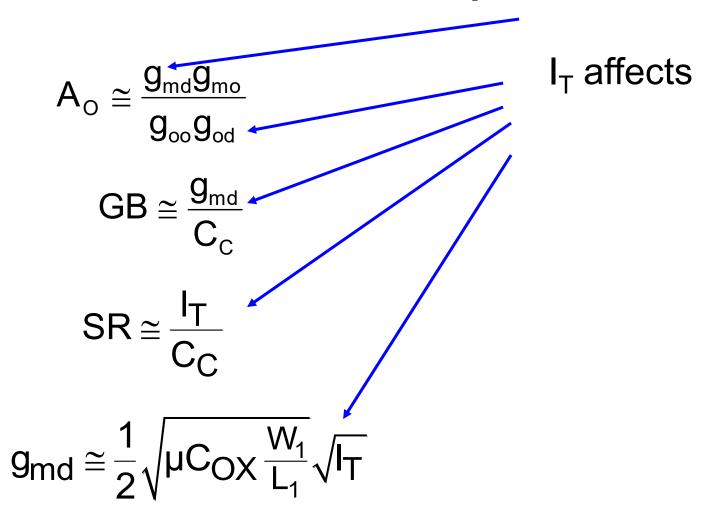

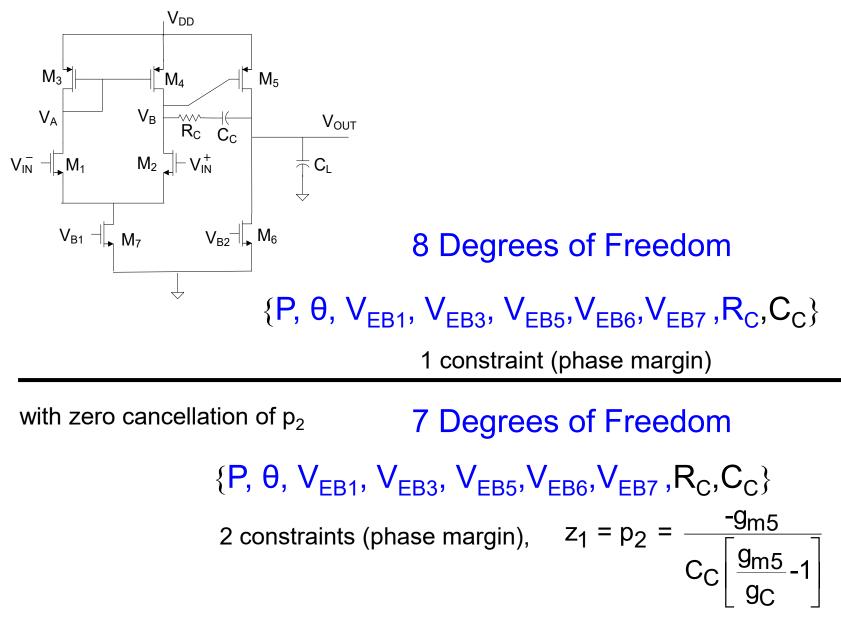

## Natural Parameter Space for the Two-Stage Amplifier Design

$S_{NATURAL} = \{W_1, L_1, W_3, L_3, W_5, L_5, W_6, L_6, W_7, L_7, I_T, I_{D6}, C_c\}$

• • • • • Review from last lecture .• • • • •

## Parameter Inter-dependence

## Practical Set of Design Parameters

$S_{\text{PRACTICAL}} = \{P, \theta, V_{\text{EB1}}, V_{\text{EB3}}, V_{\text{EB5}}, V_{\text{EB6}}, V_{\text{EB7}}\}$

7 degrees of freedom!

- P : total power dissipation

- $\theta$  = fraction of total power in second stage

- $V_{EBk}$  = excess bias voltage for the k<sup>th</sup> transistor

- Phase margin constraint assumed (so C<sub>c</sub> not shown in DoF)

## **Example for Design Procedure**

Summary of Design Procedure for This Set of Specifications and this Architecture:

- 1. Choose channel length

- 2. Select:  $V_{EB3}$ ,  $V_{EB5}$ ,  $V_{EB6}$

- 3. Select: V<sub>EB1</sub>

- 4. Select: V<sub>EB7</sub>

- 5. Choose P to satisfy power constraint

- 6. Choose  $\theta$  to meet GB constraint

- 7. Compensation capacitance  $\rm C_{\rm C}$

- 8. Calculate all transistor sizes

- 9. Implement structure, simulate, and make modifications if necessary guided by where deviations may occur

Note: Though not shown, this design procedure was based upon looking at the set of equations that must be solved and developing a sequence to solve these equations. It may not always be the case that equations can be solved sequentially.

Note: Different specification requirements (constraints) will generally require a different design procedure

• • • • • Review from last lecture .• • • • •

### Power distribution between stages

Note: Optimum power split for previous example was for dominant pole compensation in first stage. Results may be different for Miller compensation or for output compensation

For first-stage compensation capacitor with compensation criteria  $p_2=3\beta A_0 p_1$ :

$$GB = \frac{\left(\lambda_{p} + \lambda_{n}\right)\theta P}{V_{DD} 3\beta C_{L}}$$

For Miller Compensation with RHP zero and arbitrary Q compensation criteria:

$$GB = \frac{P(1-\theta)}{V_{DD}V_{EB1}C_C} = \frac{PQ^2 (2\theta V_{EB1} - \beta(1-\theta) |V_{EB5}|)^2}{C_L \beta 2\theta V_{EB1}^2 |V_{EB5}| V_{DD}}$$

By taking derivative of GB wrt  $\theta$ , it can be easily shown that the derivative is positive in the interval  $0 < \theta \le 1$  indicating that for a given P, want to make  $\theta$  close to 1 to maximize GB

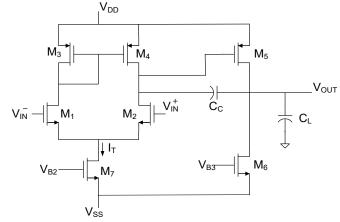

#### Basic Two-Stage Op Amp

- Why does the RHP zero limit performance?

- Can anything be done about this problem ?

- Why is this not 3<sup>rd</sup> order since there are 3 caps ?

#### Why does the RHP zero limit performance ?

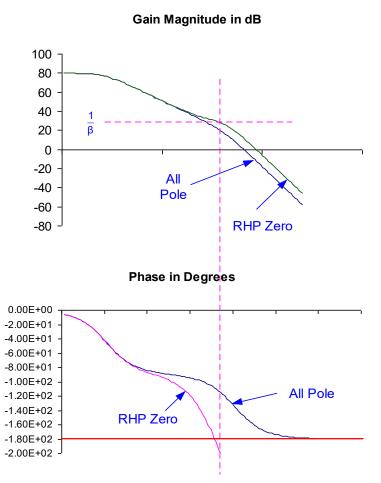

$p_1$ = -1,  $p_2$ = -1000,  $z_x$ ={none, +250}

In this example:

- accumulate phase shift and slow gain drop with RHP zeros

- effects are dramatic

#### Why does the RHP zero limit performance ?

Gain Magnitude in dB 100 80 60 40 20 ß 0 -20 All -40 Pole -60 LHP and -80 **RHP** Zero Phase in Degrees 0.00E+00 -2.00E+01 -4.00E+01 -6.00E+01 LHP Zero -8.00E+01 -1.00E+02 All Pole -1.20E+02 -1.40E+02 **RHP** Zero -1.60E+02 -1.80E+02 -2.00E+02

p<sub>1</sub>=1, p<sub>2</sub>=1000, z<sub>x</sub>={none,250,-250}

In this example:

- accumulate phase shift and slow gain drop with RHP zeros

- loose phase shift and slow gain drop with LHP zeros

- effects are dramatic

What causes the Miller compensation capacitor to create a RHP zero?

At low frequencies,  $V_{OUT}/V_d$  is positive but at high frequencies it becomes negative

Alternately, C<sub>C</sub> provides a feed-forward inverting signal from the input to the first stage output which also becomes the second stage output

Feed-forward paths create zeros in the gain transfer function !

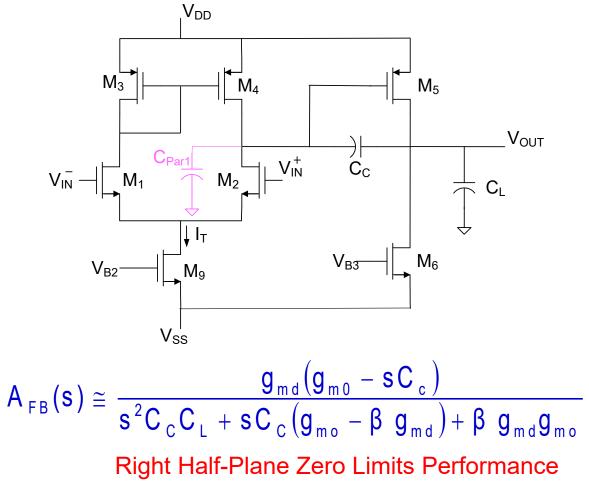

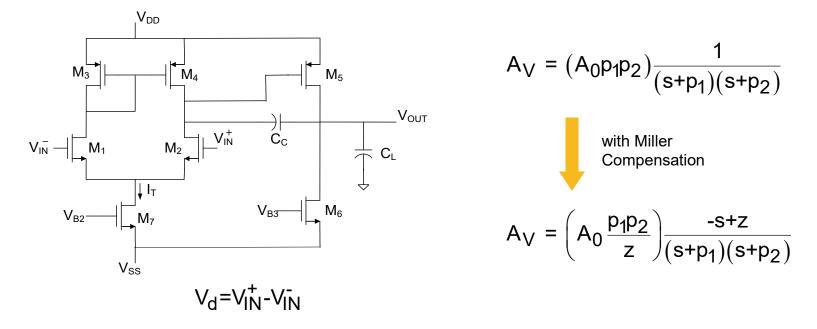

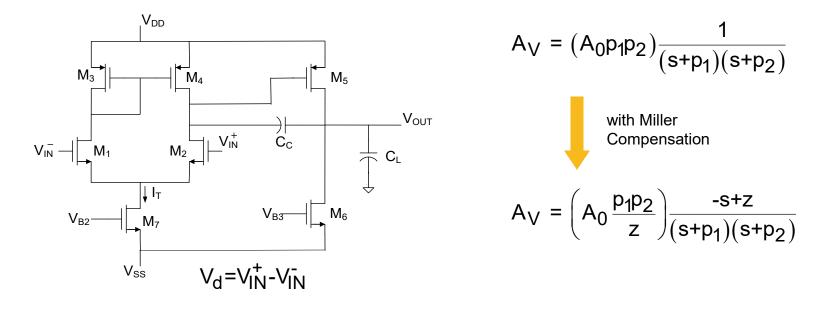

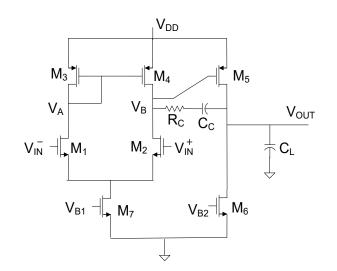

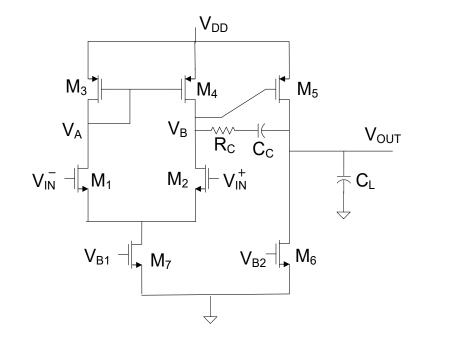

## Two-stage amplifier

(with RHP Zero Compensation)

What can be done to remove the RHP zero?

Alternately, C<sub>C</sub> provides a feed-forward inverting signal from the input to the first stage output which also becomes the second stage output

Break the feed-forward path from the output of the first stage to the output of the second stage at high frequencies

**Right Half-Plane Zero Limits Performance**

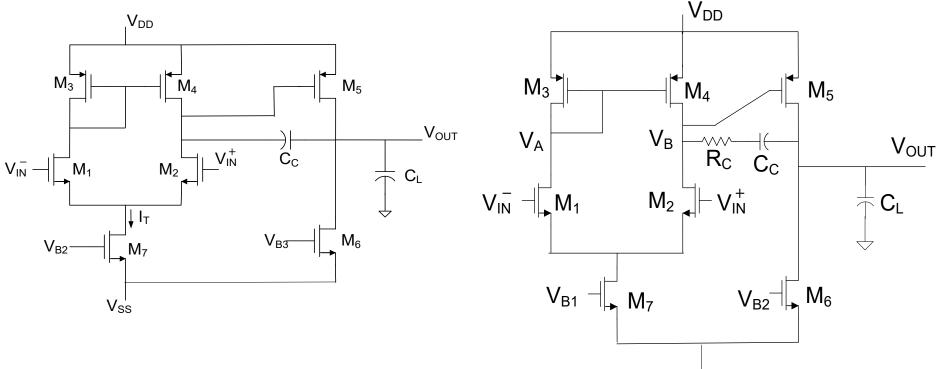

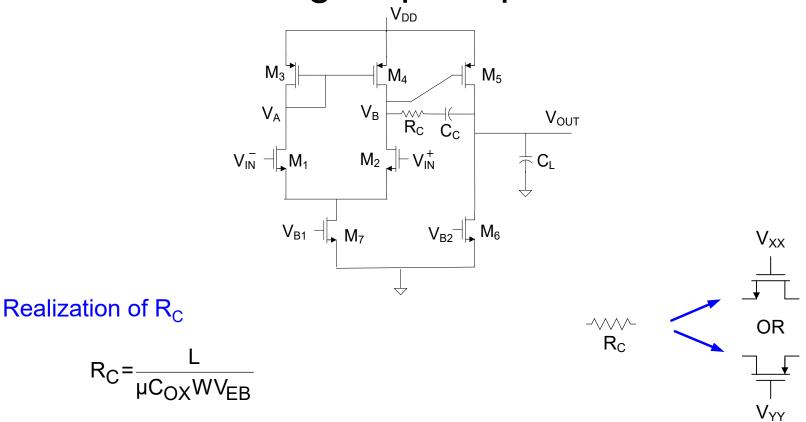

Will show zero can be moved to Left Half-Plane  $R_c$  realized with single triode region device

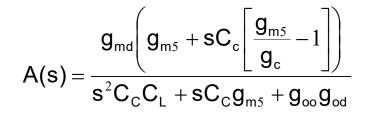

#### Analysis almost by inspection:

$$A(s) = \frac{g_{md}(g_{m5} - sC_{c})}{s^{2}C_{c}C_{L} + sC_{c}g_{m5} + g_{oo}g_{od}}$$

$$\frac{1}{sC_c} \Rightarrow \frac{1}{sC_c} + R_c$$

$$sC_c \Rightarrow \frac{sC_c}{1+sC_cR_c}$$

$$A(s) = \frac{g_{md} \left( g_{m5} + sC_{c} \left[ \frac{g_{m5}}{g_{c}} - 1 \right] \right)}{s^{2}C_{c}C_{L} + sC_{c}g_{m5} + g_{oo}g_{od}}$$

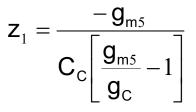

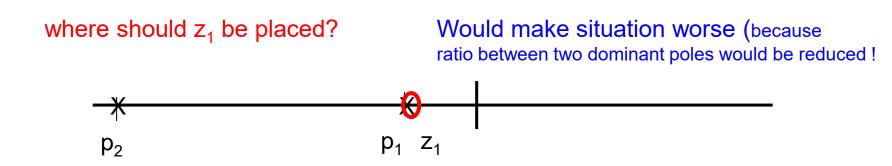

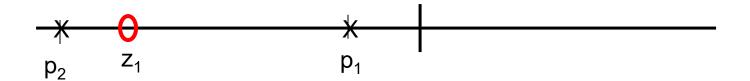

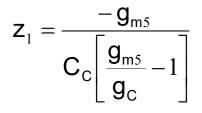

$$\mathbf{z}_{1} = \frac{-\mathbf{g}_{m5}}{\mathbf{C}_{c} \left[\frac{\mathbf{g}_{m5}}{\mathbf{g}_{c}} - 1\right]}$$

$z_1$  location can be programmed by  $R_C$ If  $g_c > g_{m5}$ ,  $z_1$  in RHP and if  $g_c < g_{m5}$ ,  $z_1$  in LHP  $R_C$  has almost no effect on  $p_1$  and  $p_2$

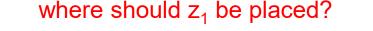

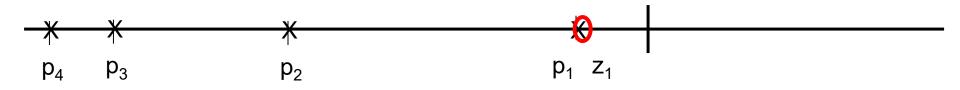

# Two-stage amplifier with LHP Zero Compensation $A(s) = \frac{g_{md} \left( g_{m5} + sC_{c} \left[ \frac{g_{m5}}{g_{c}} - 1 \right] \right)}{s^{2}C_{c}C_{1} + sC_{c}g_{m5} + g_{oo}g_{od}}$ $\mathbf{Z}_{1} = \frac{\mathbf{g}_{m5}}{\mathbf{C}_{c} \left[ \frac{\mathbf{g}_{m5}}{\mathbf{q}_{c}} - 1 \right]}$ $p_1 = -\frac{g_{o1} + g_{o5}}{C_c \left(\frac{g_{m5}}{g_{m5}}\right)}$ $p_2 = -\frac{g_{m5}}{C_L}$ $Z_1$ $p_1$ $p_2$

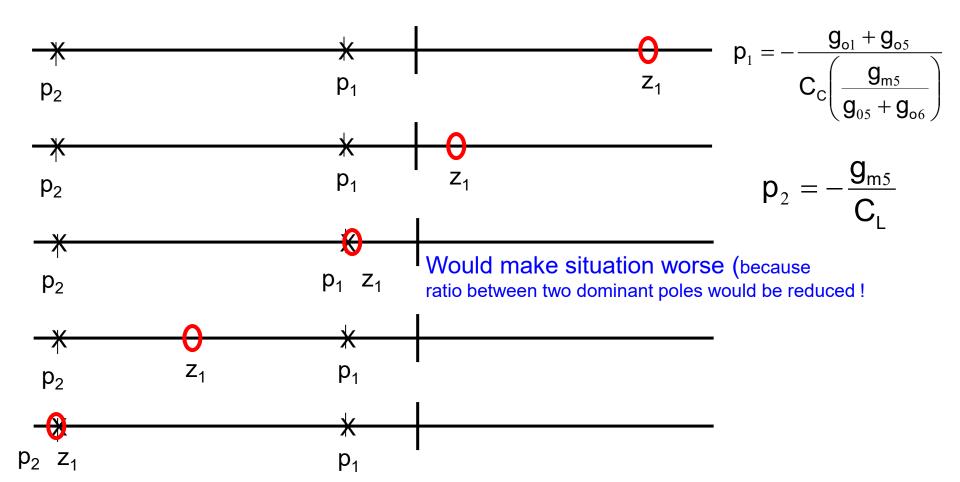

where should  $z_1$  be placed?

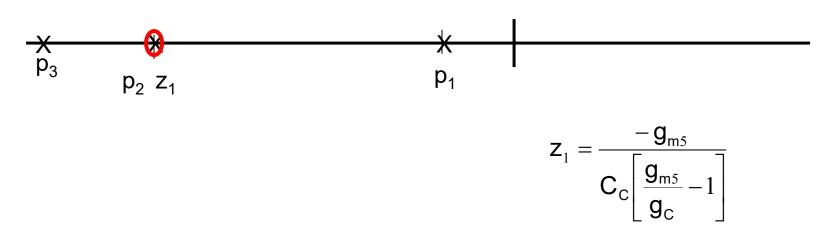

## Two-stage amplifier with LHP Zero Compensation $\mathbf{Z}_{1} = \frac{-\mathbf{g}_{m5}}{\mathbf{C}_{c} \left[ \frac{\mathbf{g}_{m5}}{\mathbf{q}} - 1 \right]}$

Other parasitic poles, at higher frequencies are present and not too much larger than  $p_2!$

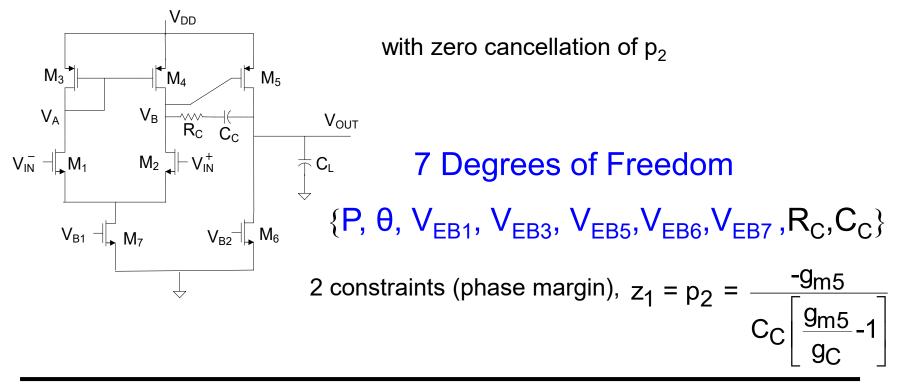

$z_1$  often used to cancel  $p_2$

Can reduce size of required compensation capacitor a) eliminates RHP zero b) increases spread between p<sub>1</sub> and p<sub>3</sub>

Improves phase margin

Design formulations easily extend to this structure

Analytical formulation for compensation requirements not easy to obtain (must consider at least 3<sup>rd</sup> –order poles and both T(s) and poles not mathematically tractable)

$C_{\rm C}$  often chosen to meet phase margin (or settling/overshoot) requirements after all other degrees of freedom used with computer simulation from magnitude and phase plots

#### Basic Two-Stage Op Amp with LHP zero

#### Basic Two-Stage Op Amp with LHP zero

#### Design Flow:

- 1. Ignore  $R_c$  and design as if RHP zero is present

- 2. Pick R<sub>c</sub> to cancel p<sub>2</sub>

- 3. Adjust  $p_1$  (i.e. change/reduce  $C_C$ ) to achieve desired phase margin (or preferably desired closed-loop performance for desired  $\beta$ )

#### Basic Two-Stage Op Amp with LHP zero

Transistors in triode region Very little current will flow through transistors (and no dc current)  $V_{DD}$  or GND often used for  $V_{XX}$  or  $V_{YY}$  $V_{BQ}$  well-established since it determines  $I_{Q5}$ Using an actual resistor not a good idea (will not track  $g_{m5}$  over process and temp)

## **Two-Stage Amplifiers**

#### Loop Gain Analysis

- Loop Gain

- Loading of A and  $\beta$  networks

- Breaking the Loop (with appropriate terminations)

- Biasing of Loop

- Simulation of Loop Gain

- Open-loop gain simulations

- Systematic Offset

- Embedding in closed loop

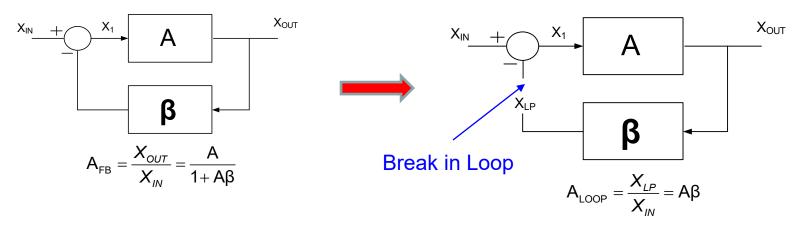

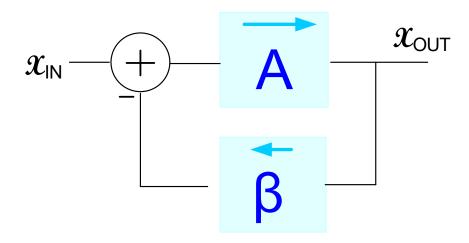

Loop Gain is a Critical Concept for Compensation of Feedback Amplifiers when Using Phase Margin Criteria (If you must!)

- Sometimes it is not obvious where the actual loop gain is at in a feedback circuit

- The A amplifier often causes some loading of the  $\beta$  amplifier and the  $\beta$  amplifier often causes some loading of the A amplifier

- Often try to "break the loop" to simulate or even calculate the loop gain or the gains A and  $\beta$

- If the loop is not broken correctly or the correct loading effects on both the A amplifier and β amplifier are not included, errors in calculating loop gain can be substantial and conclusions about compensation can be with significant error

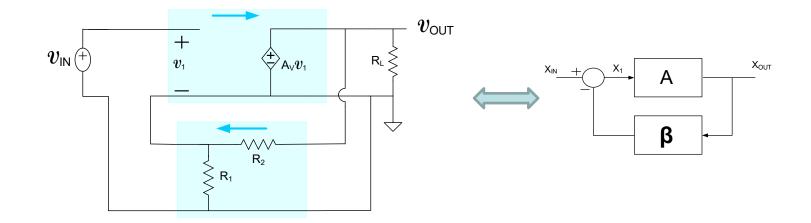

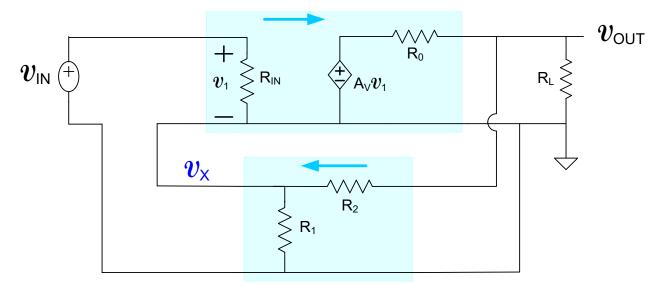

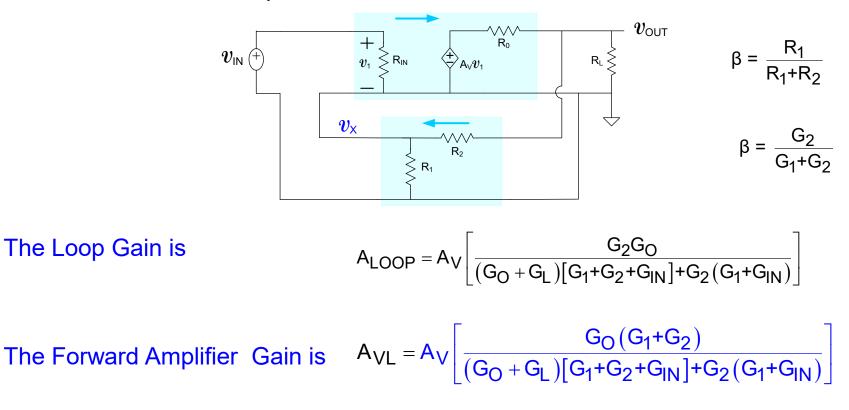

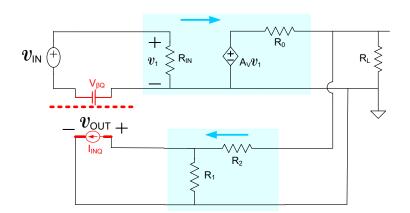

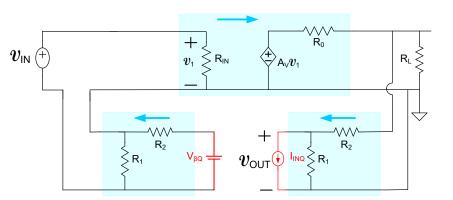

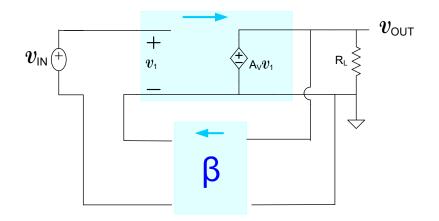

(for voltage-series feedback configuration)

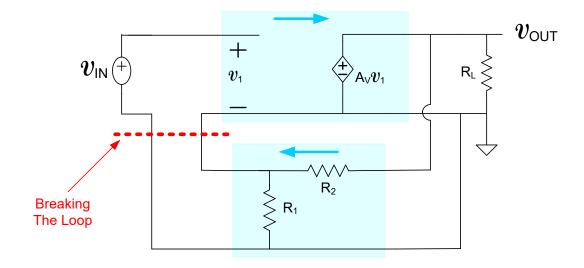

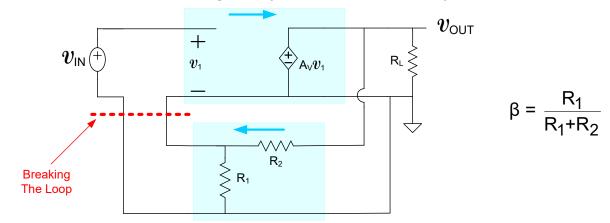

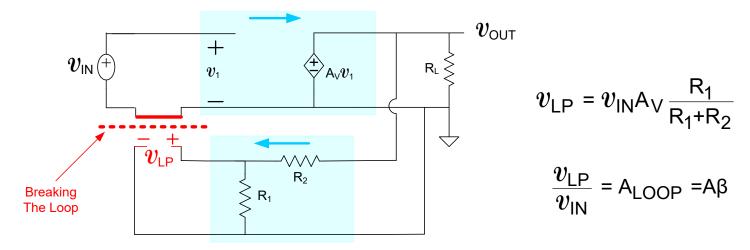

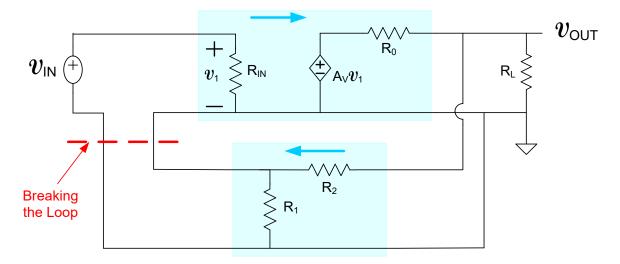

The loop is often broken on the circuit schematic to determine the loop gain

Breaking the loop to obtain the loop gain (Ideal A amplifier)

Note terminations where the loop is broken - open and short

But what if the amplifier is not ideal?

For the feedback amplifier:

$$v_{OUT}(G_{O}+G_{L}+G_{2})=v_{X}G_{2}+A_{V}v_{1}G_{O}$$

$v_{X}(G_{1}+G_{2}+G_{IN})=v_{OUT}G_{2}+v_{IN}G_{IN}$

$v_{IN}=v_{1}+v_{X}$

Solving, we obtain

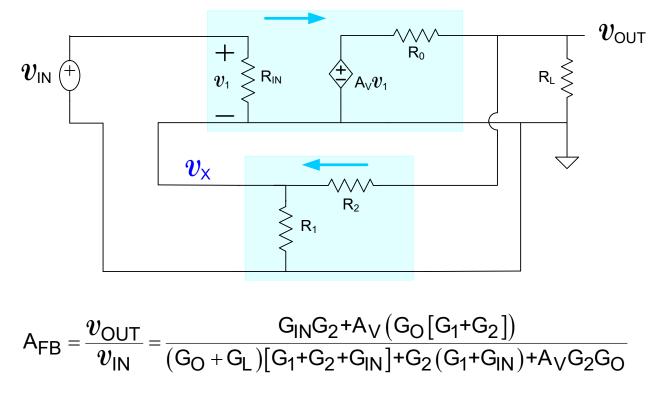

$$A_{FB} = \frac{v_{OUT}}{v_{IN}} = \frac{G_{IN}G_2 + A_V(G_O[G_1 + G_2])}{(G_O + G_L)[G_1 + G_2 + G_{IN}] + G_2(G_1 + G_{IN}) + A_VG_2G_O}$$

What is the Loop Gain ? Needed to obtain the Phase Margin !

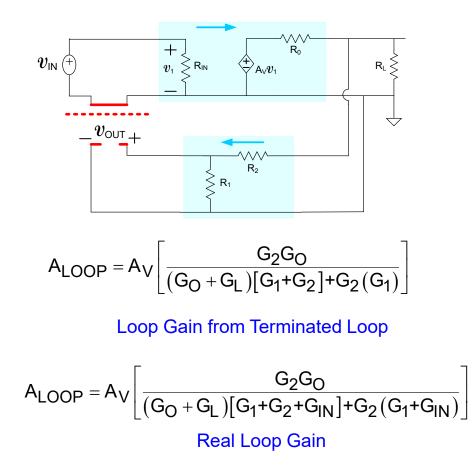

But what if the amplifier is not ideal?

What is the Loop Gain? Needed to obtain the Phase Margin!

Remember:

$$A_{FB} = \frac{F_1(s)}{1 + A\beta}$$

Characteristic Polynomial Determined by  $D(s) = 1 + A\beta$

Whatever is added to "1" in the denominator is the loop gain

But what if the amplifier is not ideal?

$$\mathsf{A}_{\mathsf{FB}} = \frac{v_{\mathsf{OUT}}}{v_{\mathsf{IN}}} = \frac{\mathsf{G}_{\mathsf{IN}}\mathsf{G}_2 + \mathsf{A}_{\mathsf{V}}(\mathsf{G}_{\mathsf{O}}[\mathsf{G}_1 + \mathsf{G}_2])}{(\mathsf{G}_{\mathsf{O}} + \mathsf{G}_{\mathsf{L}})[\mathsf{G}_1 + \mathsf{G}_2 + \mathsf{G}_{\mathsf{IN}}] + \mathsf{G}_2(\mathsf{G}_1 + \mathsf{G}_{\mathsf{IN}}) + \mathsf{A}_{\mathsf{V}}\mathsf{G}_2\mathsf{G}_{\mathsf{O}}}$$

Can be rewritten as

$$A_{FB} = \frac{\frac{G_{IN}G_2}{(G_O + G_L)[G_1 + G_2 + G_{IN}] + G_2(G_1 + G_{IN})} + A_V \left(\frac{G_O[G_1 + G_2]}{(G_O + G_L)[G_1 + G_2 + G_{IN}] + G_2(G_1 + G_{IN})}}{1 + A_V \left[\frac{G_2G_O}{(G_O + G_L)[G_1 + G_2 + G_{IN}] + G_2(G_1 + G_{IN})}\right]}$$

The Loop Gain is

$$A_{LOOP} = A_{V} \left[ \frac{G_{2}G_{0}}{(G_{0} + G_{L})[G_{1} + G_{2} + G_{IN}] + G_{2}(G_{1} + G_{IN})} \right]$$

But what if the amplifier is not ideal?

The Loop Gain is

$$A_{LOOP} = A_V \left[ \frac{G_2 G_0}{(G_0 + G_L)[G_1 + G_2 + G_{IN}] + G_2(G_1 + G_{IN})} \right]$$

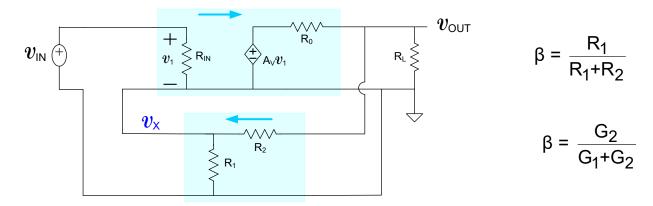

This can be rewritten as

$$A_{LOOP} = \left(A_{V}\left[\frac{G_{O}(G_{1}+G_{2})}{(G_{O}+G_{L})[G_{1}+G_{2}+G_{IN}]+G_{2}(G_{1}+G_{IN})}\right]\right)\left[\frac{G_{2}}{G_{1}+G_{2}}\right]$$

This is of the form

$$A_{LOOP} = (A_{VL}) \left[ \frac{G_2}{G_1 + G_2} \right]$$

where  $A_{VL}$  is the open loop gain including loading of the load and  $\beta$  network !

$$A_{VL} = A_{V} \left[ \frac{G_{O}(G_{1}+G_{2})}{(G_{O}+G_{L})[G_{1}+G_{2}+G_{IN}]+G_{2}(G_{1}+G_{IN})} \right]$$

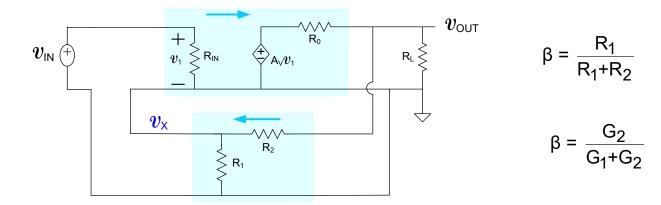

But what if the amplifier is not ideal?

Note that  $A_{VL}$  is affected by both its own input and output impedance and that of the  $\beta$  network

This is a really "messy" expression

Any "breaking" of the loop that does not result in this expression for  $A_{\rm VL}$  will result in some errors though they may be small

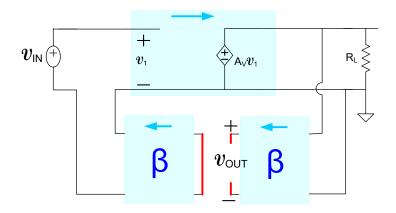

(for voltage-series feedback configuration)

But what if the amplifier is not ideal?

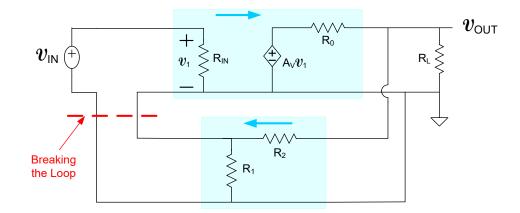

- Most authors talk about breaking the loop to determine the loop gain  $A\beta$

- In many if not most applications, breaking the loop will alter the loading of either the A amplifier or the  $\beta$  amplifier or both

- Should break the loop in such a way that the loading effects of A and  $\beta$  are approximately included

- Consequently, breaking the loop will often alter the actual loop gain a little

- Q-point must not be altered when breaking the loop (for analysis with simulator)

- In most structures, broken loop only gives an approximation to actual loop gain

- Sometimes challenging to break loop in appropriate way

(for voltage-series feedback configuration)

But what if the amplifier is not ideal?

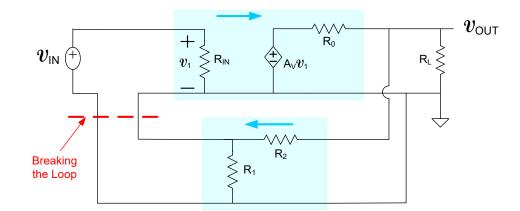

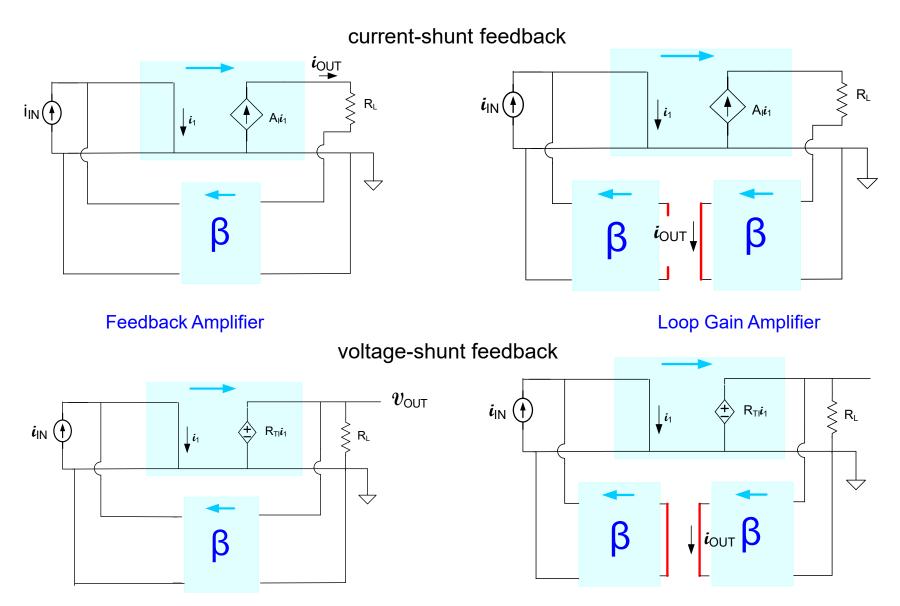

Standard Small-Signal Loop Gain Circuit

#### Standard Loop Gain Circuit including Biasing

(terminations shown in ss circuit are what is needed in the actual amplifier)

#### Loop Gain - Aβ

(for voltage-series feedback configuration)

But what if the amplifier is not ideal?

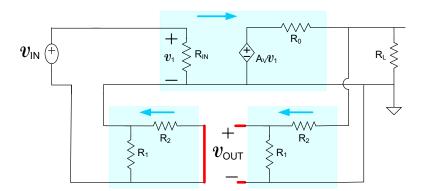

Breaking loop even with this termination will result in some error in ALOOP

#### Loop Gain - Aβ

(for voltage-series feedback configuration)

But what if the amplifier is not ideal?

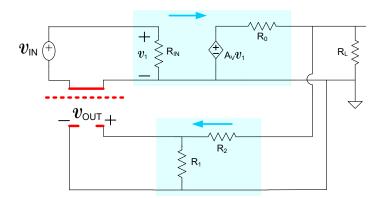

Better Standard Small-Signal Loop Gain Circuit

#### Better Loop Gain Circuit including Biasing

(terminations shown in ss circuit are what is needed in the actual amplifier)

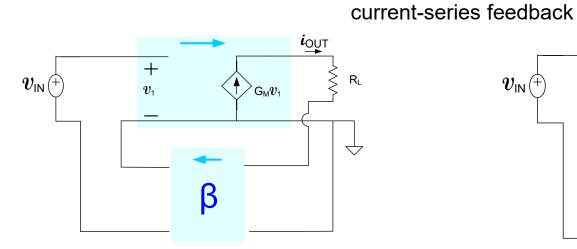

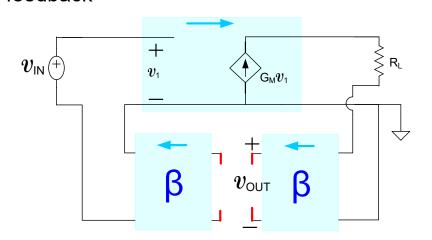

# Loop Gain - $A\beta$ for four basic amplifier types

voltage-series feedback

**Feedback Amplifier**

# Loop Gain - $A\beta$ for four basic amplifier types

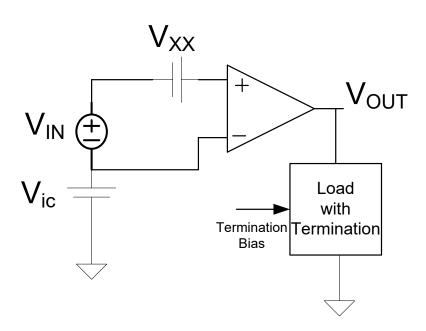

## **Open-loop gain simulations**

- Must first adjust  $V_{XX}$  to trim out any systematic offset

- Always verify all devices are operating in the desired region of operation

- If an ac input is applied to  $V_{\text{IN}},$  no information about linearity or signal swing will be obtained

- If any changes in amplifier circuit are made,  $V_{\text{XX}}$  must be trimmed again

- Include any loading including loading of beta network (with proper termination)

## **Open-loop gain simulations**

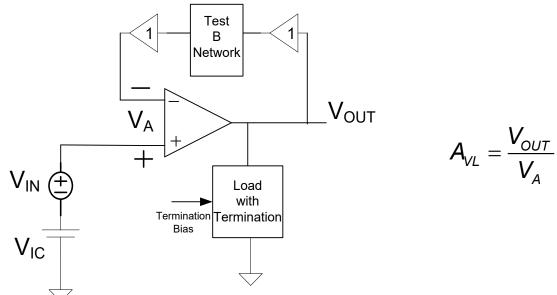

(with a closed-loop test bench)

- Stabilizes the effect of the systematic offset voltage

- Test  $\beta$  network may not be related to actual  $\beta$  at all

- Loading of actual β network included in "Load with Termination"

- Input and output buffers eliminate any loading effects of the test  $\beta$  network

- $A_V$  must be calculated from measurements of  $V_{OUT}$  and  $V_A$

- Test  $\beta$  network must be chosen so overall network is stable

Why not just use actual  $\beta$  network for test  $\beta$  network?

Actual  $\beta$  network may even be unstable before compensation is complete

### **Feedback simulations**

Why not just simulate the frequency response of the actual feedback amplifier and look at the magnitude of the gain to see if that is what we want ?

Isn't that what we really want anyway?

If the amplifier is overly underdamped or oscillatory, won't that show up anyway?

Remember, the small-signal analysis will have the same magnitude response for minimum-phase and non-minimum phase systems !

#### Tools for Helping with Amplifier Compensation

Numerous tools but generally require analytical models

Based upon testbenches using actual circuit schematics (though behavioral descriptions can be included)

#### STB (in Spectre)

The Spectre STB analysis provides a way to simulate continuous time loop gain, phase margin and gain margin without breaking the feedback loop.

In the stability analysis you are required to choose a probe from which the loop gain measurements are taken. The probes, described below, can be found in the analogLib library.

Many sources on line discussing STB analysis. (One youtube video is listed below (without assessment of either validity or quality)

https://youtu.be/L8wJhENPZNc

#### Other Methods of Gain Enhancement

Methods used so far:

Increasing the output impedance of the amplifier cascode, folded cascode, regulated cascode

Increasing the transconductance (current mirror op amp) but it didn't really help because the output conductance increased proportionally

Cascading gives a multiplicative gain effect (thousands of architectures but compensation is essential) practically limited to a two-level cascade because of too much phase accumulation **Recall:**

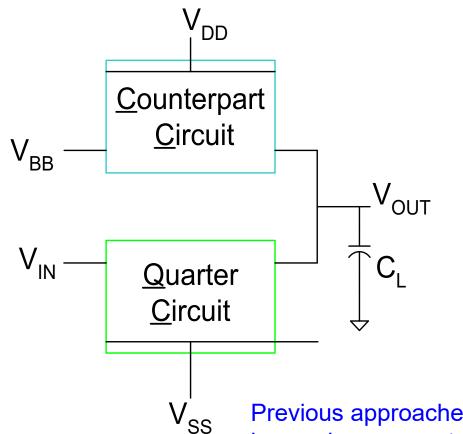

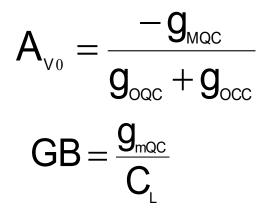

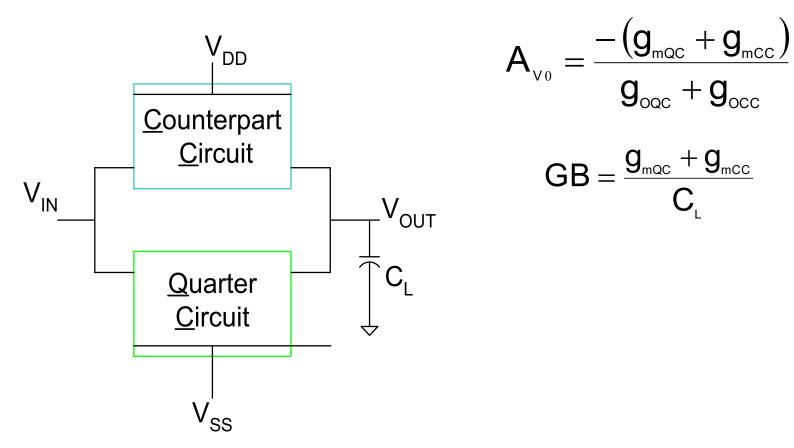

### Other Methods of Gain Enhancement

Recall:

Two Strategies:

1. Decrease denominator of  $A_{V0}$

2. Increase numerator of  $A_{V0}$

Previous approaches focused on decreasing denominator or increasing numerator with current mirror

#### **Consider now increasing numerator with excitation**

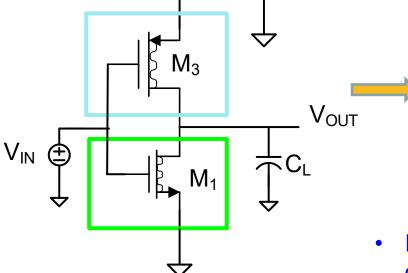

#### Other Methods of Gain Enhancement

Consider now increasing numerator by changing the excitation

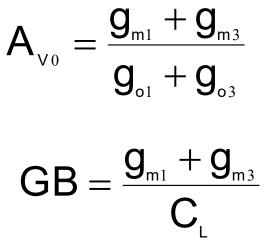

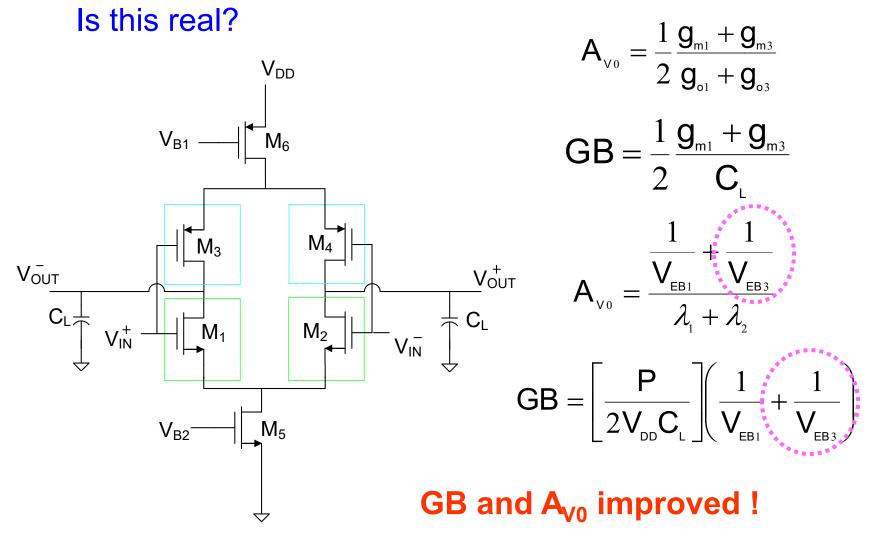

### g<sub>meq</sub> Enhancement with Driven Counterpart Circuit

Recall:

- In the small-signal parameter domain, both gain and GB appear to be enhancement

- Is this real?

Needs CMFB Circuit to  $V_{B1}$  or  $V_{B2}$

### g<sub>meq</sub> Enhancement with Driven Counterpart Circuit

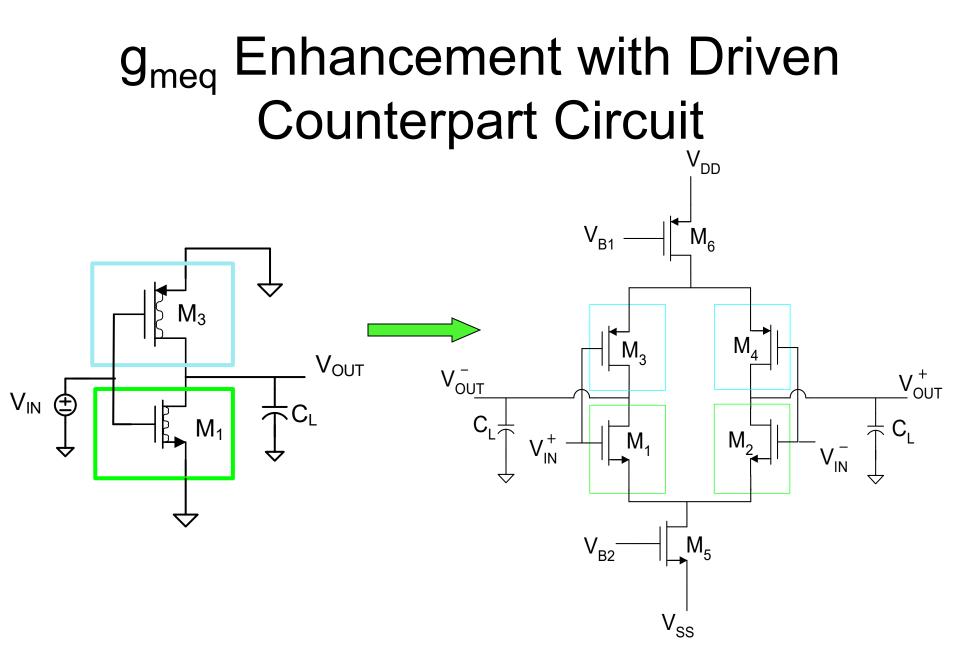

### Other Methods of Gain Enhancement

Increasing the output impedance of the amplifier cascode, folded cascode, regulated cascode

Increasing the transconductance (current mirror op amp) but it didn't really help because the output conductance increased proportionally

Driving the counterpart circuit does offer some improvements in gain

Cascading gives a multiplicative gain effect (thousands of architectures but compensation is essential) practically limited to a two-level cascade because of too much phase accumulation

## Stay Safe and Stay Healthy !

### End of Lecture 18